240530_ CPU 첫 발자국 RISC-V 기능 추가중

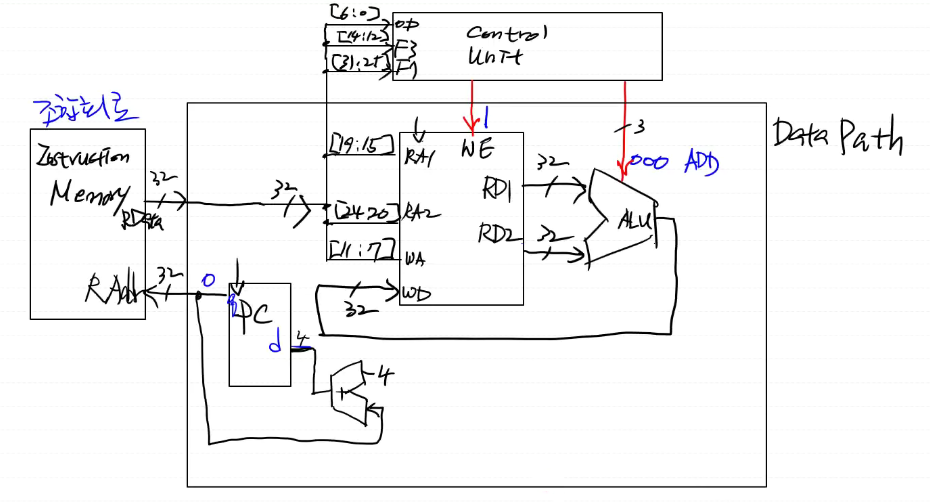

Instruction Memory 사용--> CPU

Instruction set architecture : 명령어 집합. ISA

RISC V

RV32I 버전으로.

Register File 32bit RegisterX 32개

어제 했던 R0, R1 --> X0 X1... Register의 이름

RISC-V, RV32I ISA을 Single Cycle로 구현하자.

머신코드에 대해서 어떻게 나오게 할 것인가. --> Instruction Memory

Function ? 왜씀? --> OPCODE 고정되어있어서.

OPCODE : TYPE

Instruction 에는 명령어가 이미 다 들어가 있고 우리는 주소를 쏴서 이 명령어를 출력한다.

일반적인 memory 의 하나의 크기는 1byte인데 우리껀 4byte 단위가 되어버렸다.

그래서 4 단위로 0x0---0001 ~ 0004 씩 묶어서 써야한다.

뒷 00 을 xx 로 무시하기 때문에 4개씩 받게끔 되었다.

ROM 기준에서 4줄을 한번에 먹는다.

[0], [1]을 묶어버리면 주소를 읽기도 0 1 2 3 4 로 편하게 읽어진다.

지우지 않으면 0 4 8 불편학 읽어야한다.

(2번 Shift 한 값 처럼 읽힌다.) 실제 ROM 에는 256byte가 생겨있다 --> [31:0] *4

rom[0] 값만 출력되고 있다.

ADDER 추가가 필요하다.

RegFile 값을 확인해야 저장되는 값을 볼 수 있다.

2개의 입력 --> MUX로 해결

그런데 bit가 안맞는 MUX가 나타났다. ==> bit 연산자로 bit값을 맞춘다. bit의 확장.

EXTEND 모듈에서 opcode 를 뺸 나머지를 받아서 확장.

sign bit를 포함한 확장.

instruction 의 [31:20] 을 받고 나서 확장해준다.

최상위 비트를 확장시켜야 부호가 바뀌지 않는다.

신호가 점점 많아지고 있다.

R값만 쓰던거에서 I 값이 추가되었다.